ELBRUS 48IPS

SILICON AT THE SPEED OF SOFTWARE

Design Arm amd RISC Cpu in very short time

INTRODUCE ELBRUS 48IPS

Key Features

- Architecture: “RV64GC”

- 64-bit RISC-V with 32 integer registers (I extension)

- Integer multiplication and division (M extension)

- Atomic operation support (A extension)

- Compressed mode for better code density (C extension)

- IEEE 754-2008 compliant single and double precision floating point (F+D extensions)

- Up to 4 cores in complex

- Machine, Supervisor and User modes

- 10 stage out-of-order pipeline

- Advanced branch predictor: BTB, BHT, RAS

- Sv39 Virtual Memory support

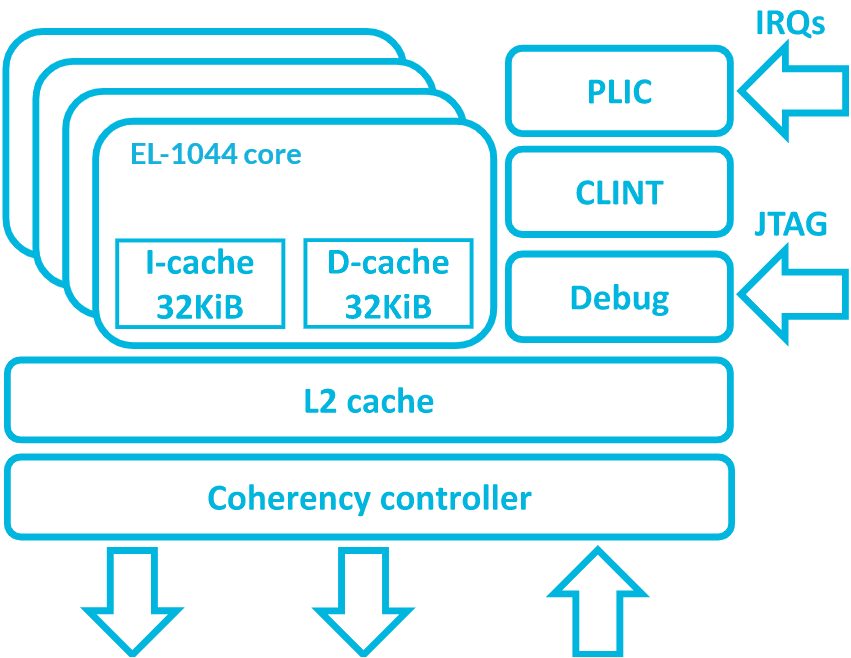

- 32 KiB 8-way L1 I-cache

- 32 KiB 8-way L1 D-cache

- Integrated debug controller

- AXI system interface

- AXI peripheral interface

- AXI front-port interface for accelerator coherent access

- 3.58 DMIPS/MHz

- 5.36 CoreMark/MHz

- 4.6 SPEC2006 INT/GHz

- 1 GHz (TSMC, 40nm G, SSG corner)

- 1.2 GHz (TSMC, 28nm HPC+, SSG corner)

Performance:

Frequency:

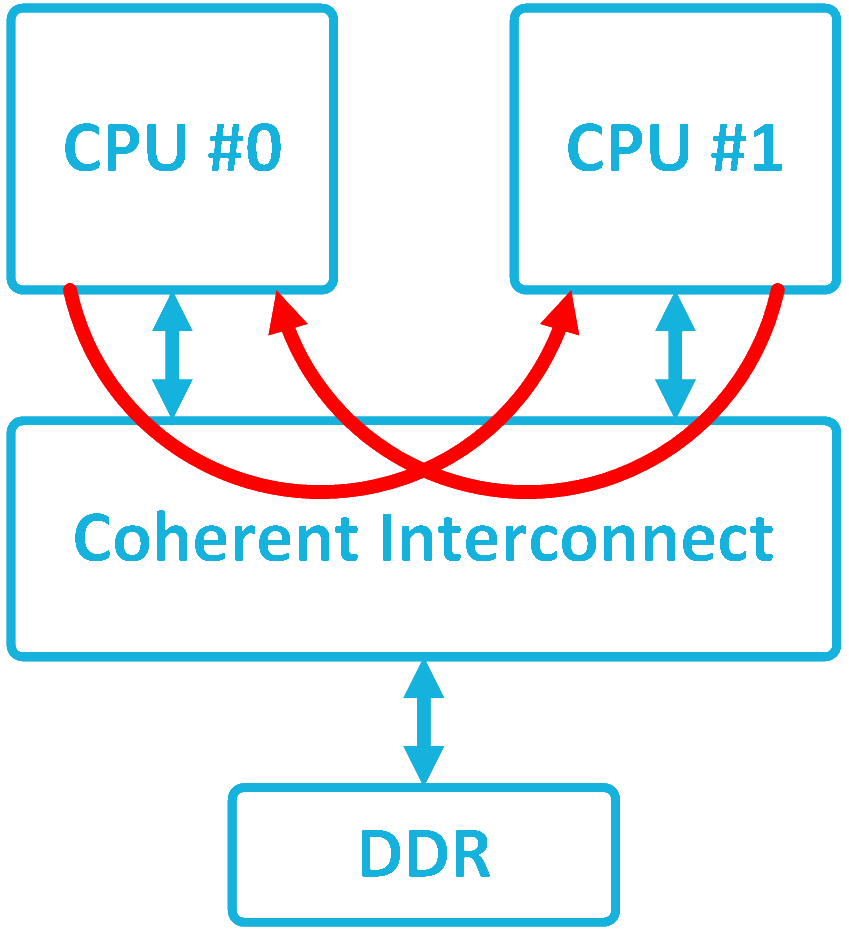

SMP support and accelerator coherency

48IPS has up to 4 cores, each with an L1 caches and a single shared L2 cache implementing fully coherent memory system. Additional coherency controller provides coherent access for accelerators via AXI front port to cached memory ranges simplifies software development and improves performance.

Development Tools

Complete set of RISC-V tools for fast and convenient software development. Compatible with upstream standard development and debug tools: OpenOCD, GCC, GDB, Eclipse. Elbrus also provides pre-configured Eclipse-based IDE with prebuilt toolchain and example projects for easy development start.

FEATURES:

Smart POS,mPOS,Tracking device,Security Level 7+,HSM,Dongle Lock,Banking system